MCIO x8 to SlimSAS x8 Cable Deployment in AI and Enterprise Platforms

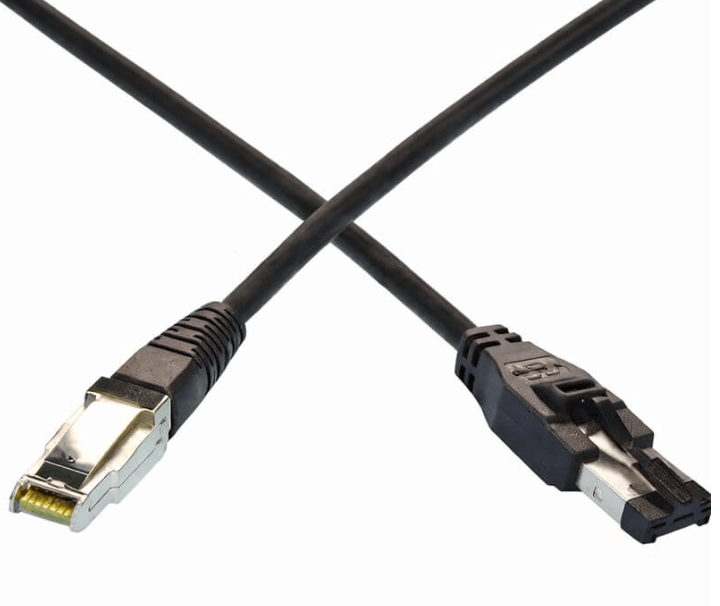

MCIO x8 to SlimSAS x8 cables are high density interconnect assemblies designed to support PCIe Gen 5 signaling between servers, accelerators, and storage subsystems. These cables bridge MCIO and SlimSAS interfaces while maintaining low latency and signal integrity at high data rates. They are commonly used in AI platforms and enterprise systems where bandwidth and port density are critical.

MCIO and SlimSAS Interface Architecture

The MCIO x8 interface supports eight high speed PCIe lanes within a compact connector designed for modern server platforms. SlimSAS x8, defined under the SFF-8654 specification, also supports eight lanes and is widely used for storage and PCIe connectivity in dense system designs.

In a combined cable assembly, each lane pair is mapped directly between MCIO and SlimSAS connectors. This preserves point to point PCIe communication and allows direct device attachment without protocol conversion.

PCIe Gen 5 Signaling and Lane Performance

PCIe Gen 5 significantly increases per lane data rates, requiring precise electrical control to maintain stable communication. Each lane operates at high transfer speeds that demand tight impedance tolerance and minimal signal loss.

MCIO to SlimSAS cables are engineered to maintain consistent differential pair characteristics across the full signal path. This supports reliable link training, low error rates, and predictable throughput between connected devices such as GPUs and NVMe storage.

Signal Integrity and Electrical Considerations

Maintaining signal integrity is essential at PCIe Gen 5 speeds. Cable assemblies must control electrical parameters across all lanes to prevent performance degradation.

Key design factors include:

- Controlled impedance across differential pairs

- Low insertion loss for signal preservation

- Effective shielding to reduce interference

- Tight skew control between paired conductors

These characteristics ensure stable link performance under varying thermal and operational conditions.

Mechanical Density and System Integration

MCIO and SlimSAS connectors enable high port density on modern server motherboards and accelerator platforms. This allows system designers to support more devices within limited physical space.

Proper cable routing is critical to avoid excessive bending and connector stress. Maintaining recommended bend radius and preventing airflow obstruction contribute to both cooling efficiency and long term reliability.

Deployment in AI and Enterprise Platforms

MCIO x8 to SlimSAS x8 cables are widely used in environments that require high bandwidth interconnects and flexible system design.

Typical deployment scenarios include:

- GPU to motherboard interconnects in AI systems

- NVMe storage expansion in enterprise servers

- Backplane connectivity in high density platforms

- Accelerator integration in compute clusters

- Test and validation platforms for PCIe devices

These use cases benefit from high throughput and efficient cable routing in compact system layouts.

Installation and Design Best Practices

Cable length should be selected based on system layout to minimize signal loss and excess slack. Ensure connectors are fully seated and properly secured.

Maintain separation between high speed signal cables and power lines where possible to reduce interference. Organized cable management improves airflow and simplifies maintenance in dense systems.

FAQ (Frequently Asked Questions)

What is the purpose of an MCIO x8 to SlimSAS x8 cable?

It connects PCIe Gen 5 devices across different connector formats while preserving direct lane communication.

Does this cable support backward compatibility with earlier PCIe versions?

Yes, compatibility depends on the connected hardware, but PCIe standards generally support backward operation.

Are these cables used only for storage systems?

No, they are also used for GPUs, accelerators, and other PCIe devices.

What limits the cable length in these assemblies?

Signal integrity constraints at PCIe Gen 5 speeds limit them to short reach applications.