How Does The I8040X2-M OCuLink Cable Enable Proper PCIe Lane Breakout

As PCIe 5.0 platforms continue to increase lane counts and per lane bandwidth, efficient lane distribution has become a critical system design requirement. In many server, storage, and embedded architectures, the number of available PCIe lanes exceeds the number of physical connectors that can be deployed. The I8040X2-M OCuLink 8x to dual 4x breakout cable addresses this imbalance by enabling a single OCuLink x8 host port to be divided into two independent x4 PCIe connections without introducing switching logic or signal conversion.

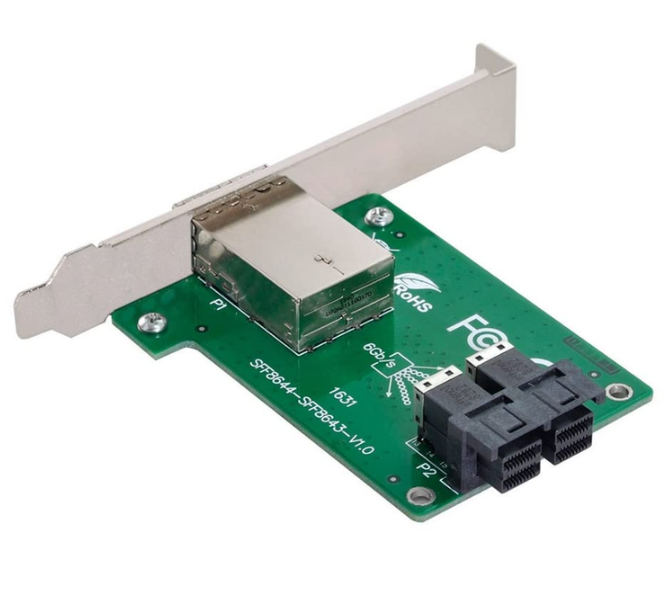

Electrical Design for Native PCIe Signaling

Proper PCIe breakout depends on preserving strict electrical characteristics across every lane. The I8040X2-M is engineered specifically for PCIe signaling rather than adapted from generic high speed cabling. Each differential pair maintains controlled impedance, consistent spacing, and matched length to support reliable PCIe 5.0 operation.

By preserving native electrical behavior from host to device, the cable allows each x4 branch to function as a direct PCIe link. There is no aggregation, retiming, or bandwidth sharing, which ensures predictable link training and stable operation at negotiated speeds.

Lane Mapping Accuracy and Standards Compliance

When a host system bifurcates an OCuLink x8 port into two x4 interfaces, correct lane ordering becomes essential. The PCIe controller expects lanes to appear in a defined sequence, and any deviation can result in reduced link width, failed enumeration, or unstable connections.

The I8040X2-M implements precise lane mapping that aligns with OCuLink and PCIe specifications. Each group of four lanes is routed to its corresponding connector with correct polarity and orientation, allowing the host firmware to recognize each downstream device as an independent PCIe endpoint.

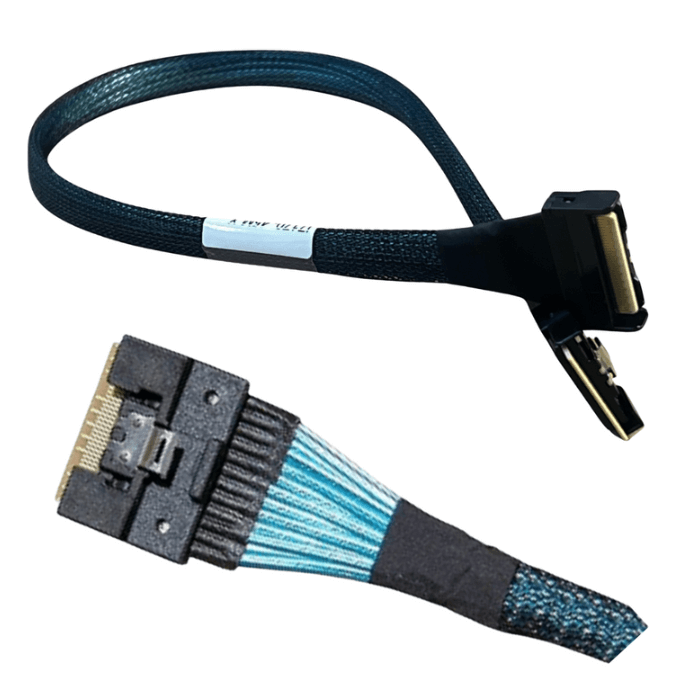

Interaction with Host Bifurcation

The cable itself does not perform lane management or switching. Instead, it relies on platform level bifurcation support provided by the CPU, chipset, and firmware. When the host is configured to split an x8 port into two x4 links, the I8040X2-M simply delivers those lanes to the appropriate devices without modification.

This approach preserves transparency at the PCIe layer. Devices enumerate directly under the host root complex, and standard PCIe configuration and error handling mechanisms remain intact.

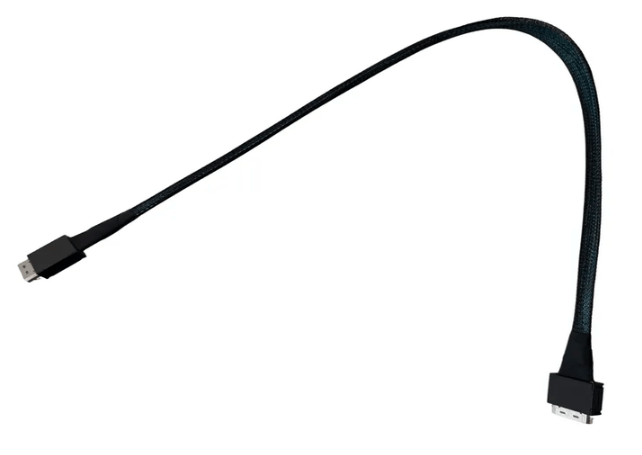

Mechanical Construction and Chassis Integration

High density systems place significant demands on internal cabling. The I8040X2-M is available in defined lengths to support clean routing within compact chassis, storage enclosures, and multi compartment server designs. Proper length selection minimizes excess slack, improves airflow, and reduces strain on connectors.

Connector retention and mechanical stability are also critical. Secure latching and consistent connector geometry help prevent intermittent connections during maintenance, transport, or vibration, which is especially important in edge and industrial deployments.

Use Cases where Proper Breakout Matters

A standards compliant breakout cable is most valuable in architectures that require direct CPU connectivity for multiple x4 devices. Typical deployments include:

-

NVMe storage servers connecting multiple x4 backplanes

-

Edge and embedded systems with limited expansion space

-

Compute platforms where PCIe switch latency is undesirable

-

Validation and test environments requiring predictable PCIe topology

In these scenarios, correct lane mapping and signal integrity are essential for reliable operation.

When this Approach is not Appropriate

An OCuLink x8 to dual x4 breakout is not suitable when a downstream device requires a full x8 link or when the host platform does not support lane bifurcation. In such cases, a native x8 connection or a PCIe switch may be required to meet system requirements.

Best Practices for Deployment

Before installation, system designers should verify that the host firmware supports OCuLink bifurcation and that the target devices are compatible with x4 links. At PCIe 5.0 speeds, careful cable routing and adherence to bend radius guidelines help preserve signal margins.

Validation testing under full load is recommended to confirm stable link training and sustained performance.

FAQ (Frequently Asked Questions)

What makes the I8040X2-M suitable for PCIe 5.0 breakout?

It is engineered with controlled impedance, accurate lane mapping, and tight pair matching to support PCIe 5.0 signaling requirements.

Does the cable perform any active PCIe functions?

No, it is a passive assembly. All PCIe logic remains on the host and device side.

Can the cable be used with non storage PCIe devices?

Yes, it supports any compatible PCIe x4 device, including accelerators and expansion modules.

Is firmware configuration required for proper operation?

Yes, the host system must be configured to bifurcate the OCuLink x8 port into two x4 interfaces.