How Can Cable Layout Be Optimized For PCIe Gen 4.0 Signal Integrity

PCIe Gen 4.0 operates at 16 GT per second per lane, leaving far less margin for loss, noise, and reflections than earlier generations. At these speeds, cable layout is known to be just as important as cable quality. Even a Gen 4 rated cable can underperform if it is routed poorly. Optimizing layout focuses on preserving impedance, minimizing noise coupling, and maintaining consistent mechanical geometry from connector to connector.

Start with Gen 4 Capable Cabling

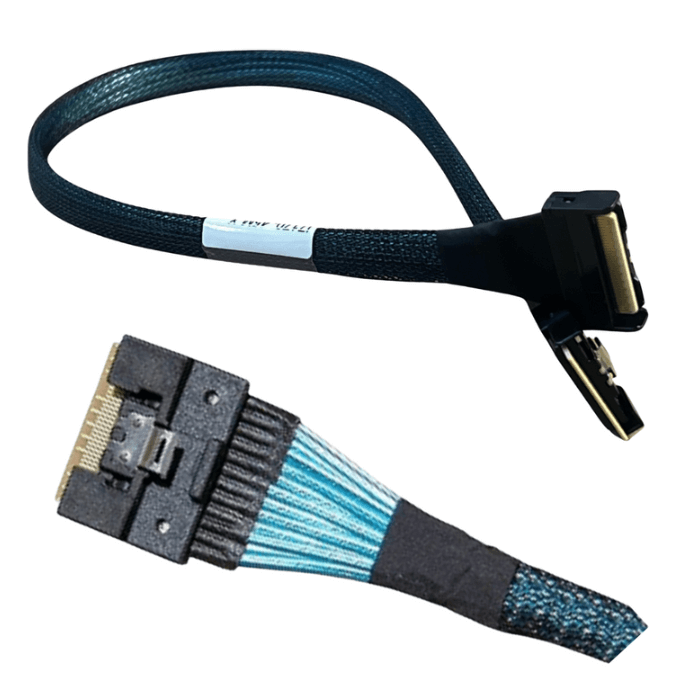

Cable layout optimization begins with selecting cables designed for PCIe Gen 4.0 operation. These assemblies use low loss materials, tight impedance control, and shielding structures intended for high frequency signaling.

Using cables that are only rated for lower speeds forces the layout to compensate for deficiencies that cannot be fully corrected. Layout optimization works best when the cable itself already meets Gen 4 electrical requirements.

Keep Cable Runs as Short as Practical

Insertion loss increases with length, and PCIe Gen 4 loss budgets are limited. Excess cable length consumes margin unnecessarily.

Use the shortest cable length that allows clean routing without strain. Avoid coiling slack inside the chassis, as loops increase loss, complicate airflow, and often introduce tight bend radii near connectors.

Maintain Proper Bend Radius Throughout the Run

Sharp bends distort the internal geometry of high speed cables. This alters impedance and increases reflections.

A general rule is to maintain a minimum bend radius of at least ten times the cable diameter. This is especially important near connector overmolds, where the cable is already mechanically constrained. Gentle, sweeping curves preserve signal integrity far better than tight turns.

Minimize Strain at Connectors

Connectors are the most sensitive transition points in the PCIe channel. Mechanical strain near the connector can introduce intermittent impedance changes that are difficult to diagnose.

Route cables so that they naturally exit the connector without pulling, twisting, or side loading. Provide gradual strain relief and avoid routing that forces the cable to immediately change direction at the connector face.

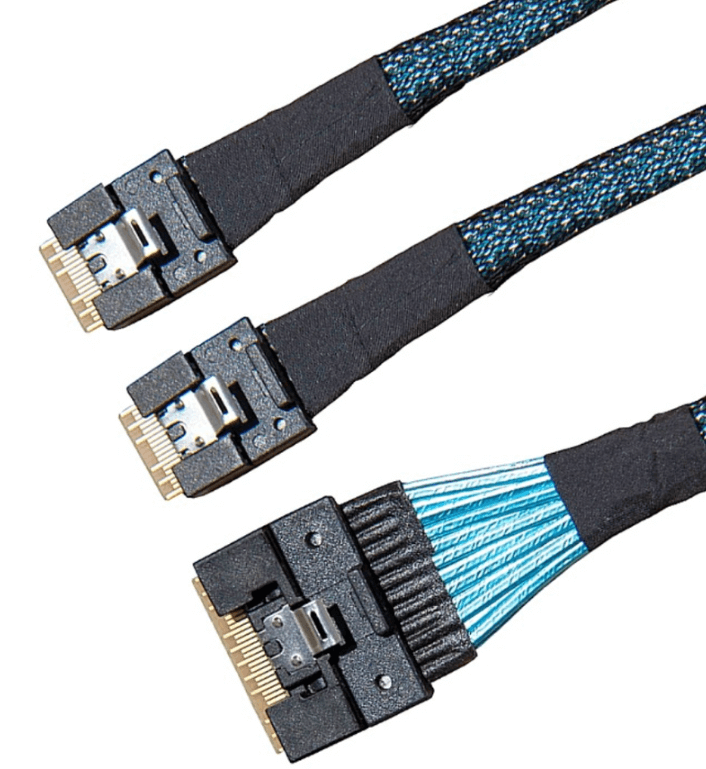

Reduce Crosstalk Between Adjacent Cables

At Gen 4 speeds, crosstalk between lanes and between neighboring cables can corrupt data when multiple links are active.

Avoid bundling high speed cables tightly together for long distances. When cables must run in parallel, leave space between them or use grounded separation. When crossing other signal paths, do so at right angles rather than running alongside them.

Keep Distance From Power and Noise Sources

Power cables, voltage regulators, fans, and motors generate electromagnetic noise that can couple into high speed data paths.

Route PCIe cables away from power distribution harnesses and switching components whenever possible. If crossings are unavoidable, cross at ninety degrees and keep the interaction as short as possible.

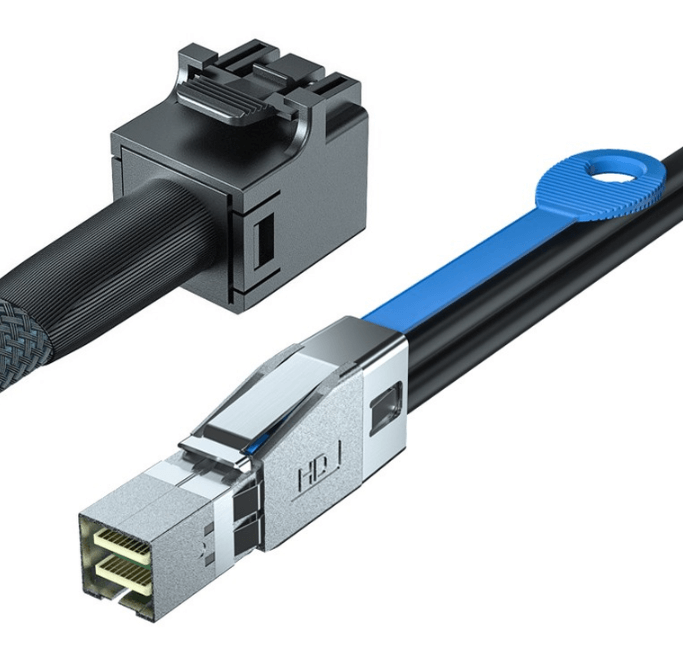

Preserve Shielding and Grounding Continuity

Shielding only works when it is continuous and properly grounded. Damaged jackets, loose connector shells, or poorly terminated shields reduce EMI protection.

Ensure connectors seat fully and make solid ground contact. Avoid pinching or compressing the cable jacket, as this can compromise shield effectiveness and alter impedance.

Avoid Unnecessary Routing Complexity

Every extra turn, branch, or connector transition increases the chance of signal degradation. Clean, direct routes are always preferable to complex paths.

Design layouts that minimize the number of connector hops and avoid unnecessary detours. In breakout cables, ensure branches are balanced and routed symmetrically to reduce skew and timing variation.

Support Airflow and Thermal Stability

Thermal variation affects electrical characteristics at high speed. Poor airflow caused by cable congestion can lead to temperature related instability in marginal links.

Optimized layouts route cables along chassis edges or designated channels, keeping airflow paths clear. This improves both cooling performance and signal stability under sustained load.

Document and Standardize Routing Paths

Consistent routing improves repeatability and reduces human error during installation or maintenance.

Use labeling, diagrams, and standardized cable paths to ensure cables are reinstalled correctly after service. Small routing changes can have measurable effects at Gen 4 speeds, so consistency matters.

Plan Layouts with Gen 5 in Mind

PCIe Gen 5 tightens margins even further. A layout that is barely stable at Gen 4 may fail at Gen 5.

When possible, apply Gen 5 routing discipline even in Gen 4 systems. Shorter runs, cleaner paths, and better separation reduce the need for rework during future upgrades.

Common Layout Mistakes to Avoid

Frequent causes of Gen 4 signal integrity issues include:

-

Tight bends near connectors

-

Excess slack bundled inside the chassis

-

Parallel routing next to power cables

-

Over tightened cable ties or clamps

-

Unsupported cable weight pulling on connectors

Avoiding these mistakes often resolves instability without changing hardware.

FAQ (Frequently Asked Questions)

Can good layout compensate for lower quality cables?

Only to a limited extent. Layout optimization cannot fully overcome excessive loss or poor impedance control.

Is bend radius really that important at Gen 4?

Yes. Even small violations can introduce reflections that reduce eye opening.

Do shorter cables always improve signal integrity?

Generally yes, as long as they are not so short that they introduce strain or sharp bends.

Why do some systems work until they heat up?

Thermal changes can push marginal channels past their stability threshold.