Why Is MCIO Positioned As The Connector For PCIe Gen 5.0 And Beyond

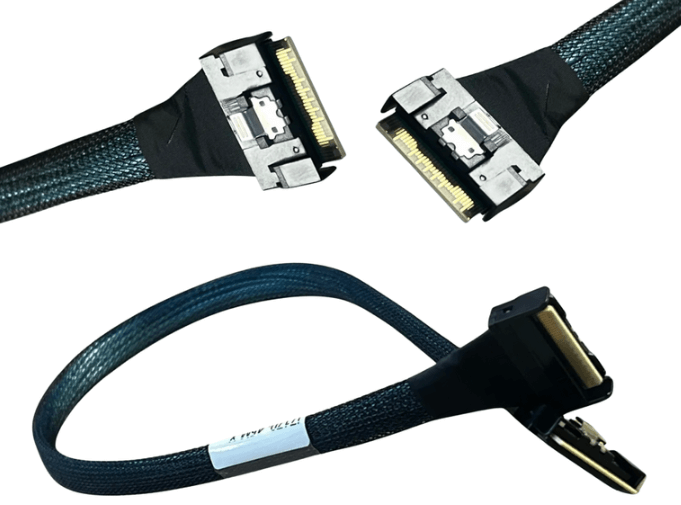

MCIO is emerging as the preferred internal connector for PCIe Gen 5.0 and future generations because it was designed specifically to solve the density, signal integrity, and scalability challenges that older connector families struggle with at very high data rates. As PCIe signaling moves from 16 GT per second in Gen 4 to 32 GT per second in Gen 5 and beyond, the physical interconnect becomes one of the most critical limiting factors. MCIO addresses those limits at the connector, cable, and system level.

Designed for Extreme Signal Integrity

PCIe Gen 5 doubles the signaling rate of Gen 4, cutting the allowable channel loss budget nearly in half. At these speeds, connectors must minimize insertion loss, reflections, and crosstalk.

MCIO was engineered with:

-

Shorter electrical paths through the connector

-

Tighter impedance control

-

Improved differential pair isolation

-

Better return loss performance

These characteristics make MCIO far more tolerant of Gen 5 signaling than legacy internal connectors that were originally designed around much lower data rates.

High Lane Density without Compromising Performance

One of MCIO’s biggest advantages is how many lanes it can support in a very small footprint.

MCIO commonly supports:

-

x4, x8, and x16 lane configurations

-

Very tight connector spacing on backplanes

-

High aggregate bandwidth without increasing board area

As servers and accelerators demand more PCIe lanes per socket, MCIO allows designers to scale bandwidth without consuming excessive PCB real estate or blocking airflow.

Optimized for Modern Backplane Architectures

MCIO aligns well with how modern servers are architected.

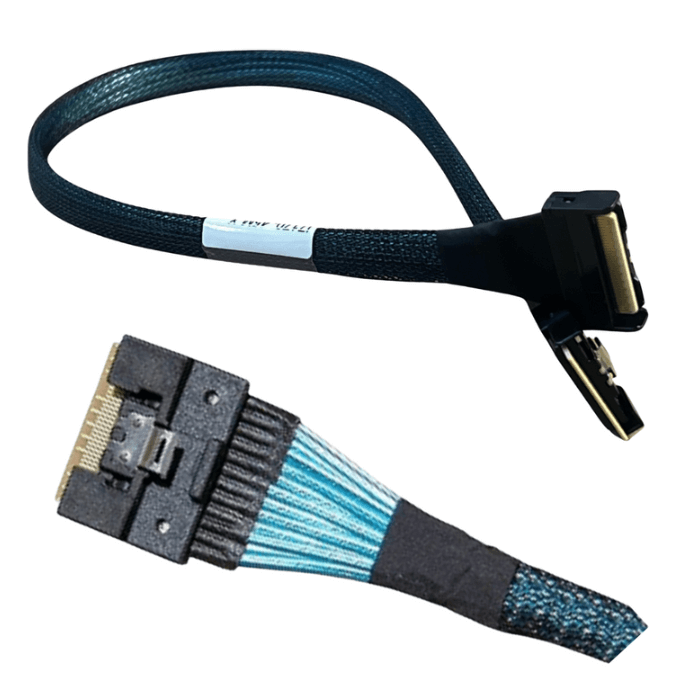

Instead of long, flexible cable runs, MCIO is often used in:

-

Short, controlled internal cable assemblies

-

Cabled backplanes with strict length budgets

-

Direct connections between switches, CPUs, and accelerators

This design philosophy matches PCIe Gen 5 requirements, where short, predictable channels are essential for stability.

Built with Future PCIe Generations in Mind

MCIO is not only Gen 5 capable, it was created with Gen 6 in mind.

As PCIe transitions to PAM4 signaling at even higher effective data rates, connectors must handle tighter eye margins and more complex equalization. MCIO’s electrical design leaves more headroom than older standards, making it adaptable to future signaling schemes without a complete connector redesign.

This forward compatibility is a major reason MCIO is favored in long lifecycle platforms.

Better Thermal and Airflow Characteristics

High speed systems concentrate both power and bandwidth in small areas. Connector bulk and cable congestion directly affect cooling.

MCIO helps by:

-

Reducing connector size compared to older interfaces

-

Allowing cleaner cable routing

-

Minimizing airflow obstruction near hot components

These thermal advantages become increasingly important as Gen 5 and Gen 6 devices push higher power envelopes.

Strong Adoption by OEMs and Hyperscalers

MCIO adoption is being driven by large scale system designers rather than niche applications.

Hyperscalers and OEMs favor MCIO because it offers:

-

Consistent performance across dense layouts

-

Better scalability for multi generation roadmaps

-

Simplified backplane and switch designs

This momentum accelerates ecosystem maturity, increasing availability of cables, connectors, and validation data.

Multi Protocol Capability Adds Flexibility

Like other modern connector standards, MCIO is not limited to a single protocol.

Depending on implementation, MCIO can carry:

-

PCIe

-

NVMe

-

SAS

This flexibility allows platform designers to standardize on a single physical connector while supporting multiple device types, reducing complexity in manufacturing and service.

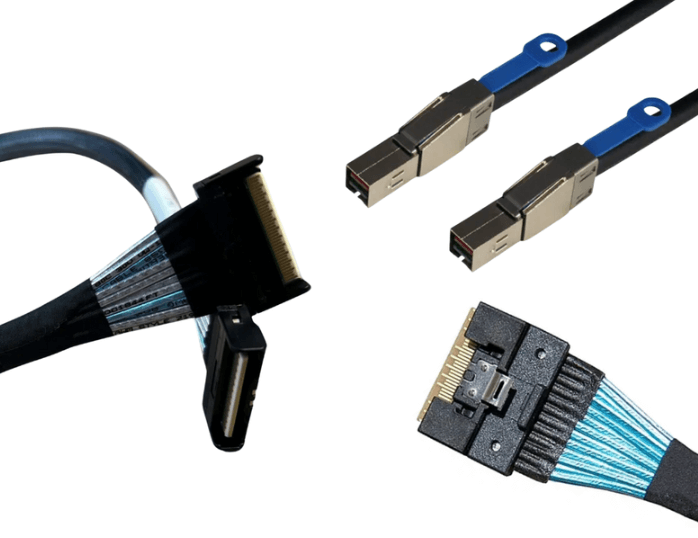

Why Older Connectors Struggle at Gen 5 and Beyond

Legacy standards such as HD MiniSAS and even SlimSAS were not originally optimized for Gen 5 signaling budgets.

Common limitations include:

-

Higher insertion loss at the connector interface

-

Lower lane density per connector

-

Less margin for PAM4 signaling

While some can be extended to Gen 5 in limited scenarios, they lack the native headroom MCIO provides.

Where MCIO Delivers the Most Value

MCIO is especially well suited for:

-

PCIe Gen 5 server backplanes

-

PCIe switch fabrics

-

AI and accelerator dense platforms

-

High performance NVMe storage systems

-

Designs targeting Gen 6 readiness

In these environments, MCIO simplifies scaling while preserving signal integrity.

Practical Takeaway

MCIO is positioned as the connector for PCIe Gen 5.0 and beyond because it was designed specifically for high speed, high density, and forward scalability. Its electrical performance, compact form factor, thermal advantages, and future readiness align with where PCIe is headed, not where it has already been. For new designs targeting longevity and maximum performance, MCIO is not just an upgrade, it is an architectural shift.

FAQ (Frequently Asked Questions)

Is MCIO required for PCIe Gen 5?

No, but it offers significantly more margin and scalability than older connectors.

Can MCIO support earlier PCIe generations?

Yes. It can carry Gen 3 and Gen 4 signals, though its advantages are most apparent at Gen 5 and above.

Will MCIO completely replace SlimSAS?

In many Gen 5 and Gen 6 designs, yes. SlimSAS may remain in moderate density systems.

Does MCIO eliminate the need for retimers?

No. It reduces loss and improves margin, but long channels may still require signal conditioning.