Why Does PCIe Gen 5.0 Place Stricter Demands On High Speed Cables Than Gen 4.0?

PCIe Gen 5.0 significantly raises the performance ceiling for modern servers, storage platforms, and accelerator based systems. By doubling the signaling rate of Gen 4.0, it enables much higher bandwidth per lane, but it also reduces the margin for electrical error. These higher speeds expose physical limitations in cabling, connectors, and routing that were manageable at Gen 4.0 but become critical at Gen 5.0.

The Impact of Doubling The Signaling Rate

PCIe Gen 4.0 operates at 16 GT per second per lane, while PCIe Gen 5.0 increases that rate to 32 GT per second. Although this appears to be a simple doubling, the electrical consequences are far more complex.

At higher frequencies, signals attenuate more quickly as they travel through conductors. Loss mechanisms such as skin effect and dielectric loss become more pronounced, reducing signal amplitude and eye opening. This makes it harder for receivers to reliably distinguish between logic states, especially over longer cable runs.

Reduced Signal Integrity Margins

As data rates increase, the timing window for valid signal sampling becomes narrower. This leaves less tolerance for noise, jitter, and skew between differential pairs. Small imperfections in impedance, connector transitions, or cable geometry that were acceptable at Gen 4.0 can cause link instability at Gen 5.0.

Because of this, PCIe Gen 5.0 systems require cables with tighter impedance control, more consistent pair spacing, and higher quality shielding to minimize crosstalk and reflections.

Insertion Loss and Channel Budgets

PCIe specifications define a maximum allowable channel loss budget that includes PCB traces, connectors, and cables. While Gen 4.0 allows a relatively forgiving loss budget, Gen 5.0 tightens these limits considerably.

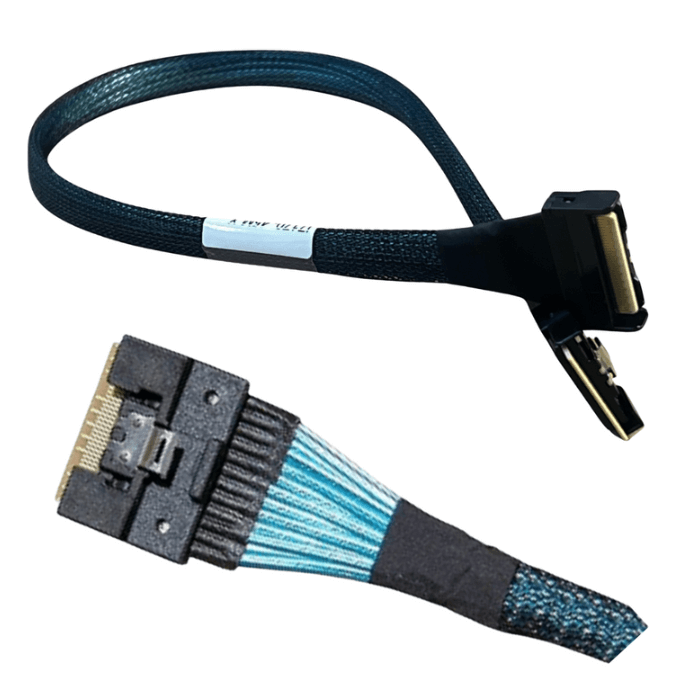

Cables used at Gen 5.0 must exhibit lower insertion loss per unit length. This often means shorter cable lengths, improved conductor materials, and advanced dielectric formulations. In some designs, cable length that was acceptable at Gen 4.0 must be reduced to maintain Gen 5.0 compliance.

Crosstalk and Electromagnetic Coupling

At higher signaling frequencies, electromagnetic coupling between adjacent pairs increases. In dense cable assemblies, this can lead to crosstalk that distorts signals and increases error rates.

Gen 5.0 cabling must address this through improved shielding strategies, optimized pair orientation, and careful internal construction. Without these measures, crosstalk can exceed acceptable thresholds and prevent stable link training.

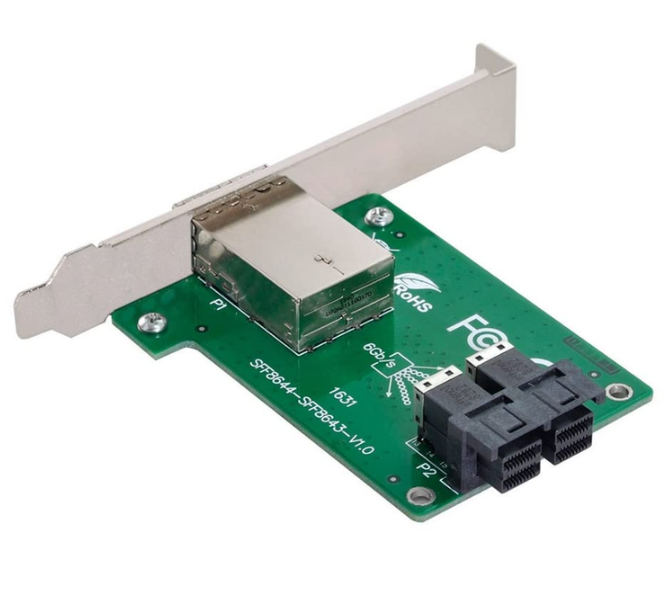

Connector and Transition Sensitivity

Connectors play a larger role in signal degradation at Gen 5.0 speeds. Every connector introduces impedance discontinuities and potential reflections. As frequencies rise, these effects become more severe.

Gen 5.0 capable cable assemblies require connectors designed specifically for high frequency operation, with tighter mechanical tolerances and smoother electrical transitions. Legacy connectors that performed well at Gen 4.0 may fail to meet Gen 5.0 requirements even if the cable itself is upgraded.

Equalization and System Complexity

PCIe Gen 5.0 relies more heavily on transmitter and receiver equalization to compensate for channel loss. While equalization can recover degraded signals, it has limits. Excessive loss or noise cannot be corrected entirely through signal processing.

This places greater responsibility on the physical channel, including the cable, to deliver a clean signal baseline. Poor quality cabling increases system complexity and can reduce interoperability between components.

Practical Design Implications

In practical terms, these stricter demands mean that not all Gen 4.0 rated cables can be reused for Gen 5.0 systems. Designers must evaluate cable length, construction quality, connector compatibility, and validation data when planning upgrades.

In many cases, Gen 5.0 designs favor shorter internal links, next generation connector standards, and cables that have been explicitly tested at 32 GT per second signaling rates.

FAQ (Frequently Asked Questions)

Can PCIe Gen 4.0 cables work at Gen 5.0 speeds?

Some may function at reduced lengths, but most are not guaranteed to meet Gen 5.0 signal integrity requirements.

Why does cable length matter more at Gen 5.0?

Higher frequencies experience greater attenuation, which reduces the allowable distance before signal quality degrades.

Is shielding more important for Gen 5.0 cables?

Yes. Improved shielding helps control crosstalk and external noise that become more disruptive at higher speeds.

Do Gen 5.0 systems always require new connectors?

Not always, but many designs adopt connectors optimized for higher frequency performance to improve reliability.